Ion-Implanted Breakdown Region

Low Voltage Overshoot under Surge

V<sub>DRM</sub>

٧

58

275

Precise and Stable Voltage

Device

'4070

'4350

### **BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTORS**

# TISP4xx0L3LM Overvoltage Protector Series

#### LM Package (Top View)

MD4XATA

NC - No internal connection on pin 2

Ring-Tip Protection ......TISP4350L3LM Electronics Protection .....

V<sub>(BO)</sub>

v

70

350

Rated for UL 1950, ITU-T and TIA/EIA-IS-968

| Surge<br>Type | Standard               | Wave<br>Shape | I <sub>TSP</sub><br>A |  |

|---------------|------------------------|---------------|-----------------------|--|

| Α             | TIA/EIA-IS-968         | 10/160        | 50                    |  |

|               | (formerly FCC Part 68) | 10/560        | 30                    |  |

| В             | TIA/EIA-IS-968         | 9/720         | 40                    |  |

| В             | UL 1950/ ITU-T K.21    | 10/700        | 40                    |  |

#### Description

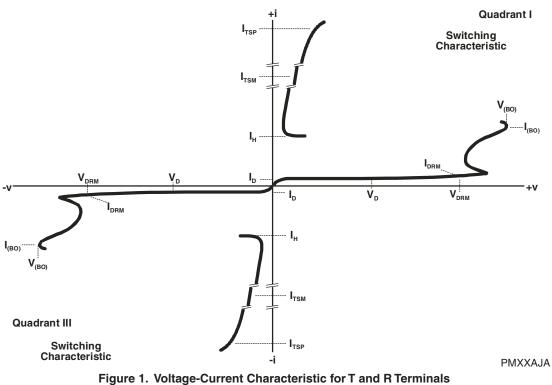

These devices are designed to limit overvoltages on the telephone line. Overvoltages are normally caused by a.c. power system or lightning flash disturbances which are induced or conducted on to the telephone line. A single device provides 2-point protection and is typically used for the protection of 2-wire telecommunication equipment (e.g. between the Ring to Tip wires for telephones and modems). Combinations of devices can be used for multi-point protection (e.g. 3-point protection between Ring, Tip and Ground).

The protector consists of a symmetrical voltage-triggered bidirectional thyristor. Overvoltages are initially clipped by breakdown clamping until the voltage rises to the breakover level, which causes the device to crowbar into a low-voltage on state. This low-voltage on state causes the current resulting from the overvoltage to be safely diverted through the device. The high crowbar holding current prevents d.c. latchup as the diverted current subsides. These protectors are guaranteed to voltage limit and withstand the listed lightning surges in both polarities. After a Type A surge (200 A, 10/160, and 100 A, 10/560) the equipment is allowed to be non-operational or operational. For an operational pass, series resistance must be added to reduce the Type A currents to within the TISP4xxxL3LM ratings (50 A, 10/160 and 30 A, 10/560). Alternatively, a series fuse with an I<sup>2</sup>t greater than 0.45 A<sup>2</sup>s and less than 5.6 A<sup>2</sup>s could be used to give a non-operational pass. After a Type B surges the equipment must be operational. As the TISP4xxxL3LM has a current rating of 40 A, will survive both Type B surges, metallic (25 A, 9/720) and longitudinal (37.5 A, 9/720), giving an operational pass to Type B surges.

For metallic protection, the TISP4350L3LM is connected between the Ring and Tip conductors. For longitudinal protection two TISP4350L3LM protectors are used; one between the Ring conductor to ground and the other between the Tip conductor to ground. The FCC Part 68 B type ringer has voltages of 56.5 V d.c. and up to 150 V rms a.c., giving a peak voltage of 269 V. The TISP4350L3LM will not clip the B type ringing voltage as it has a high impedance up to 275 V.

The TISP4070L3LM should be connected after the hook switch to protect the following electronics. As the TISP4070L3LM has a high impedance up to 58 V, it will switch off after a surge and not be triggered by the normal exchange battery voltage.

#### How To Order

| Device     | Package Type             | Carrier   | Quantity | Order As       |

|------------|--------------------------|-----------|----------|----------------|

| TISP4070L3 | LM (Straight Lead DO-92) | Bulk Pack | 2000     | TISP4070L3LM-S |

| TISP4350L3 | LM (Straight Lead DO-92) | Bulk Pack | 2000     | TISP4350L3LM-S |

#### TISP4xx0L3LM Overvoltage Protector Series BOURNS®

### Absolute Maximum Ratings, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                                                                                                                                                      | Symbol | Value            | Unit           |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|----------------|------|

| Repetitive peak off-state voltage '4070   '4350                                                                                                                                                             |        |                  | ± 58<br>± 275  | V    |

| Non-repetitive peak on-state pulse current (see Notes 1 and 2)<br>10/160 (TIA/EIA-IS-968 (formerly FCC Part 68), 10/160 μs voltage wave shape)                                                              |        |                  | 50             |      |

| 5/310 (ITU-T K.21, 10/700 voltage wave shape)<br>5/320 (TIA/EIA-IS-968 (formerly FCC Part 68), 9/720 μs voltage wave shape)<br>10/560 (TIA/EIA-IS-968 (formerly FCC Part 68), 10/560 μs voltage wave shape) |        | I <sub>TSP</sub> | 40<br>40<br>30 | A    |

| Non-repetitive peak on-state current (see Notes 2 and 3)<br>50/60 Hz, 1 s                                                                                                                                   |        |                  | 4              | A    |

| Initial rate of rise of on-state current, Linear current ramp, Maximum ramp value < 38 A                                                                                                                    |        |                  | 250            | A/μs |

| Junction temperature                                                                                                                                                                                        |        |                  | -40 to +150    | °C   |

| Storage temperature range                                                                                                                                                                                   |        |                  | -65 to +150    | °C   |

NOTES: 1. Initially, the TISP4xxxL3LM must be in thermal equilibrium with  $T_J = 25 \ ^\circ\text{C}$

The surge may be repeated after the TISP4xxxL3LM returns to its initial conditions.

EIA/JESD51-2 environment and EIA/JESD51-3 PCB with standard footprint dimensions connected with 5 A rated printed wiring track widths. Derate current values at -0.61 %/°C for ambient temperatures above 25 °C.

### Electrical Characteristics, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Parameter         |                                            | Test Conditions                                                                                                                                                             |                                              | Min  | Тур                              | Max                              | Unit  |

|-------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------|----------------------------------|----------------------------------|-------|

| I <sub>DRM</sub>  | Repetitive peak off-<br>state current      | $V_{D} = V_{DRM}$                                                                                                                                                           | $T_A = 25 \degree C$<br>$T_A = 85 \degree C$ |      |                                  | ±5<br>±10                        | μΑ    |

| V <sub>(BO)</sub> | Breakover voltage                          | dv/dt = $\pm 250$ V/ms, R <sub>SOURCE</sub> = 300 Ω (4070)<br>(4350)                                                                                                        |                                              |      |                                  | ±70<br>±350                      | V     |

| V <sub>(BO)</sub> | Breakover voltage                          | $dv/dt = \pm 1000 V/\mu s$ , Linear voltage ramp,<br>Maximum ramp value = $\pm 500 V$<br>di/dt = $\pm 20 A/\mu s$ , Linear current ramp,<br>Maximum ramp value = $\pm 10 A$ | '4070<br>'4350                               |      |                                  | ±78<br>±359                      | V     |

| I <sub>(BO)</sub> | Breakover current                          | dv/dt = $\pm 250$ V/ms, R <sub>SOURCE</sub> = 300 $\Omega$                                                                                                                  |                                              | ±40  |                                  | ±250                             | mA    |

| V <sub>T</sub>    | On-state voltage                           | I <sub>T</sub> = ±5 A, t <sub>W</sub> = 100 μs                                                                                                                              |                                              |      |                                  | ±3                               | V     |

| Ι <sub>Η</sub>    | Holding current                            | I <sub>T</sub> = ±5 A, di/dt = - /+ 30 mA/ms                                                                                                                                |                                              | ±120 |                                  | ±350                             | mA    |

| dv/dt             | Critical rate of rise of off-state voltage | Linear voltage ramp, Maximum ramp value < 0.85 V <sub>DRM</sub>                                                                                                             |                                              | ±5   |                                  |                                  | kV/μs |

| I <sub>D</sub>    | Off-state current                          | $V_D = \pm 50 \text{ V}$                                                                                                                                                    | $T_A = 85 \ ^\circ C$                        |      |                                  | ±10                              | μΑ    |

| C <sub>off</sub>  | Off-state capacitance                      |                                                                                                                                                                             | '4070<br>'4350                               |      | 40<br>38<br>31<br>26<br>24<br>20 | 50<br>48<br>39<br>33<br>30<br>25 | pF    |

# TISP4xx0L3LM Overvoltage Protector Series

## BOURNS®

#### **Thermal Characteristics**

| Parameter        |                                         | Test Conditions                                                                                   |  | Тур | Max | Unit |

|------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------|--|-----|-----|------|

| R <sub>eJA</sub> | Junction to free air thermal resistance | EIA/JESD51-3 PCB, $I_T = I_{TSM(1000)}$ ,<br>T <sub>A</sub> = 25 °C, (see Note 4)                 |  |     | 120 | °C/W |

|                  |                                         | 265 mm x 210 mm populated line card,<br>4-layer PCB, $I_T = I_{TSM(1000)}$ , $T_A = 25 \degree C$ |  | 57  |     | 0,11 |

NOTE 4: EIA/JESD51-2 environment and PCB has standard footprint dimensions connected with 5 A rated printed wiring track widths.

# TISP4xx0L3LM Overvoltage Protector Series

## BOURNS®

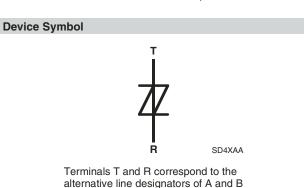

**Parameter Measurement Information**

All Measurements are Referenced to the R Terminal

# TISP4xx0L3LM Overvoltage Protector Series

BOURNS®

### **MECHANICAL DATA**

**Device Symbolization Code**

Devices will be coded as below.

| Device     | Symbolization<br>Code |  |  |

|------------|-----------------------|--|--|

| TISP4070L3 | 4070L3                |  |  |

| TISP4350L3 | 4350L3                |  |  |

"TISP" is a trademark of Bourns, Ltd., a Bourns Company, and is Registered in U.S. Patent and Trademark Office. "Bourns" is a registered trademark of Bourns, Inc. in the U.S. and other countries.