# **DEVICE MOUNTING TECHNOLOGY**

#### **SURFACE MOUNT**

Surface mounting is still the most common and economical approach for many applications. Bourns® Microelectronic Module products offer the latest in surface mount technology:

- Chip sizes to 0201

- SOIC, PLCC, TSOP, QFP to 0.012 " (0.3 mm)

- · CSP, odd form components

- BGA: 0.5 mm pitch, underfill

- · Inert reflow

- Lead free solder capability

- · Passive component test

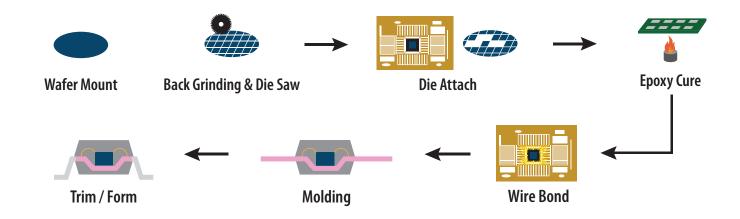

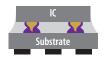

### COB (CHIP ON BOARD)

This proven technology provides an intermediate level of miniaturization, advantages of in-process test and repair, and is designed to withstand certain harsh environments such as automotive applications. Bourns® Microelectronic Module products offer the latest in chip & wire technology:

- Die mounting (Face-up die from 6-12 inch wafer)

- Size 0.17 mm to 50.0 mm

- · Thickness 0.02 mm to 7.0 mm

- Flip chip (Face-down die from wafer)

- Die size: 0.8 mm to 50.0 mm

- Die thickness: 0.10 mm to 5.0 mm

- Min. bump size: 50 μm 250 μm

- Min. bump pitch:  $100 \mu m 500 \mu m$  (others on request)

- Placement accuracy XY:  $\pm 10 \mu m @ 3s$ ; Theta:  $\pm 0.15 ° @ 3s$

- Non-conductive epoxy and conductive epoxy

- Sinter paste with high thermal conductivity ≥ 200 w/mk)

- Epoxy void: <5 %</li>

- BLT (mil): 0.3 2 mil

- Epoxy coverage: > 80 %

- Epoxy bleed out (mil): ≤3 mil

- Eutectic, 5 µm accuracy

### DEVICE MOUNTING TECHNOLOGY

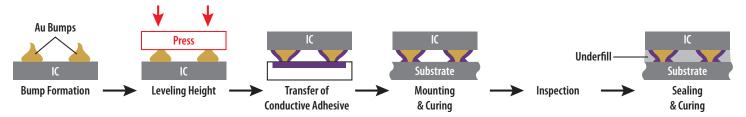

#### **FLIP CHIP MOUNTING**

This process provides the ultimate opportunity for package miniaturization, minimization of conductor lengths and size reduction in high speed, high frequency applications.

#### Full Process for Stud Bump Bonding

- Epoxy coverage is not less than 75 % of die area.

- Transparent die with no less than 50 % of the area bonded.

- Die that appears to be obviously tilted (i.e., less than 10 degrees) with respect to the package cavity.

- Die misalignment is less than 25 % of the ball of flip chip.

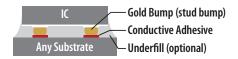

# ANISOTROPIC ADHESIVE ATTACHMENT (Z-AXIS CONDUCTIVE EPOXY)

- Ideal for PCB and flex circuits

- High I/0

- · Tight pitch

- · Cost-effective flip chip solution

- Utilizes off-the-shelf wire bondable ICs

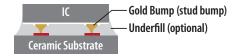

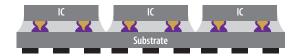

#### STUD BUMP BONDING

- Ideal for high I/O flip chip to ceramic substrate

- · Mid-process replacement of faulty chips

- · Underfill required

- · Proven technology with reliability data

- Utilizes off-the-shelf wire bondable ICs

# THERMAL-SONIC BONDING (GOLD-TO-GOLD INTERCONNECT)

- Ideal for high frequency applications and MEMs to ceramic substrates

- I/O limited to ~ 32 or less

- · Underfill optional

- · Low temperature process

- · Lead free

#### **SOLDER MOUNTING**

- Standard flip chip technology

- Solder bumped devices

- · Optional underfill

- · Z-axis control for ultimate strength

- · High volume cost-effective solution

# **DEVICE MOUNTING TECHNOLOGY**

#### **SOLDER MOUNTING**

- CSP (Chip Scale Packaging): smallest package for surface mounting

- MCM (Multichip Modules): smallest package for multichip hybrid

- SIP (Single Inline Packaging): 0.050 ", 0.100 " and 1.8 mm

- DIP (Dual Inline Packaging): 0.100 "

- BGA (Ball Grid Array)

- QFP (Quad Flat Pack)

- J-Leads in dual or quad configuration: 0.050  $\mbox{\it "},$  0.075  $\mbox{\it "}$  and 0.100  $\mbox{\it "}$

- Mini-DIL

- T0-cans

- Butterfly

- · Hermetic seal

#### **WIRE BONDING**

- Gold wire bonding: 12.5 60  $\mu m$  (0.5 to 2.4 mil) wire to 80  $\mu m$  (3.2 mil) pitch

- Aluminum wedge bonding: 125 380 μm (5 to 15 mil) wire for high current/power applications

- Copper wire bonding: 12.5 60 μm

- Ribbon bonding: Size from 6 μm X 35 μm to 25 μm X 250 μm

Min. loop length 70  $\mu$ m (2.8 mil), Min. loop height 50  $\mu$ m (2 mil), Placement accuracy  $\pm$  7.6  $\mu$ m ( $\pm$  0.3 mil)

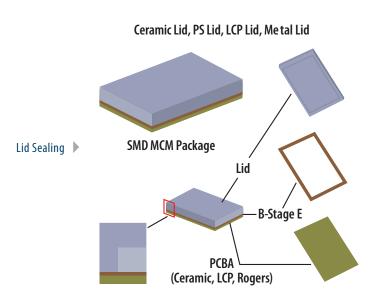

### GLOB TOP, DAM & FILL, LID SEALING, SEAM SEALING

■ Glob Top, Dam & Fill

Seam Sealing

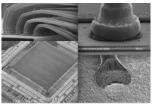

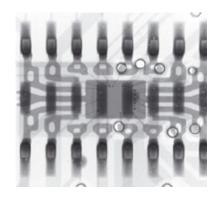

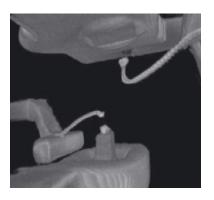

## X-RAY & CT TECHNOLOGY

The X-ray machine enables insights into printed circuit board assemblies, components, or electrical devices in an intuitive, non-destructive inspection process. The X-ray systems are supplied with a highly accurate sample manipulator with an optional precision CT rotate axis. Specifically designed for use in production lines and failure analysis laboratories, the X-ray machine can be configured with a choice of premium system components to optimize the performance for your needs.

▲ 3D Image on a Broken Bonding Wire

QFN Top View

### **TEST & MEASUREMENT**

Bourns test and measurement group makes detailed electrical evaluations and provides accurate test results for customers.

#### **TEST CAPABILITY & EXPERIENCE**

- ANSI ESD 20.20-2014 certification continuously from year 2011 to present.

- GPS transceiver, Wi-Fi, wireless headphone power protection combo modules: 1.50 GHz  $\sim$  2.50 GHz

- Satellite communication transceiver: 3 W @ 28 GHz ~ 32 GHz

- Optical driver amplifier modules: 12 Gb to 40 Gb

- Power amplifier: 2 W @ 25 GHz ~ 44 GHz

- In process test, ICT (In-circuit test), VCT (Voltage circuit test) and FCT (Function circuit test)

- Test instrument: Microwave analog signal generator N5183A & HMC-T2240, Power meter E4419B, Power sensor N8485A, Network analyzer E5071C/ZNB4, High accuracy multimeter HP/Agilent 3458A, Source meter Keithley24X0 series, Power supply HP/Agilent 66XX & 67XX series, Impedance analyzer HP4192A, High accuracy LCR meter E4980A, Audio analyzer HP8903B, Signal generator HP3325A/HP8112A, Timer/counter HP5335A, ICT tester AT360, Data acquisition & switch unit Agilent34970 including I/O card Agilent 34901, and so on. Note 1

RF Test System

ANSI ESD 20.20-2014 ► Certification

## THICK FILM MULTILAYER

#### SUBSTRATE MATERIALS

#### Alumina (Al203) Ceramic Substrate

- 96 % and 99.6 % Alumina content available with 0.25  $\sim$  4 mm thickness

- High level of heat dissipation (20 W/m K)

#### Aluminum Nitride (AIN) Substrate

- Highest level of heat dissipation (up to 200 W/m K) without the toxic effects of BeO

- · Coefficient of thermal expansion closely matching silicon

- Superior reliability for applications that require a high level of temperature cycling

#### **CONDUCTIVE THROUGH-HOLES**

- Multiple conductor materials available to coat, plug, or fill through-holes in the ceramic substrate (Figure 1)

- Multiple through-hole diameters from 0.20  $\sim$  1.0 mm and high density through-hole arrays are available

(Figure 1)

#### **CONDUCTORS**

- Multiple conductor materials available to allow for wire bonding, soldering, and brazing (Au, Ag, Pt and PdAg)

- · Available conductor thickness from 4 to 25 microns

- Fine line conductors available with .002 " feature width and spacing (Figure 2)

- Integrated microwave features are available: filters, inductors, micro-strips and Lange couplers

(Figure 2)

#### **DIELECTRICS**

#### **Printed Dielectric:**

- Multiple dielectric constants available (K = 6 12 standard, K = 4 available)

- Via resolution of .008 "

- Also used for crossovers, solder masks, etc.

# THICK FILM MULTILAYER

#### **INTEGRATED PASSIVE COMPONENTS**

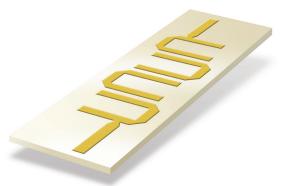

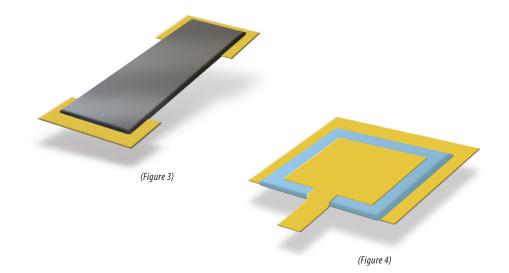

#### Thick Film Resistors (Figure 3)

- Resistance values available from 0.015 ohm/sq. to 10M ohm/sq.

- TCR of 50 ppm is available

- As fired tolerance of ± 10 %, laser trimmed values to ± 0.05 %

- More than 10 types of laser kerf for passive trim

- · Function trim for multiple hybrid module

#### Thick Film Capacitors (Figure 4)

- Dielectric constant from K = 20 to K = 1500 available

- Laser trimmed values to 5 %

### OTHER MULTILAYER OPTIONS AVAILABLE FROM BOURNS, INC:

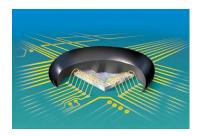

#### LTCC (Low Temperature Co-Fired Ceramic) & HTCC (High Temperature Co-Fired Ceramic)

- Extremely high interconnect density utilizing multiple laminated layers

- Coefficient of thermal expansion matched to semiconductor die for flip chip attachments

- Good thermal conductivity for power application

#### **Organic Substrates**

• FR4, FR5, LCP, Rogers, Polyamide, etc.

For any requirements outside the scope of these specifications, please contact your local Bourns representative.

#### **APPLICATIONS**

- GPS transceiver modules and sub-assemblies

- GPS, Wi-Fi, and wireless headphone power protection "all-in-one" combo modules

- Satellite-communication mechatronic transceiver (operating frequency: 32 GHz)

- High-speed optical line driver and amplifier modules (up to 64 Gbps per channel)

- 1.5+ million high-speed optical line driver and amplifier modules shipped to-date

- "Quad-Channel" E/O modulator in combination with a 4-channel line driver, tailored for 100 Gbps metro & long-haul telecommunications networking systems and applications

- Power supply module, wide adoption of AC-powered BLDC motors in aerospace/avionics industry demands for high-peak-current and low-harmonic 3-phase switch mode converter

- Smart-Transport module, wide adoption of BLDC motors in electric/hybrid vehicles, electric bicycles, battery-powered skateboards and drones should lead to new BLDC controller or power-management modules

- MEMS: VR Scanner, Pressure sensor, Humidity sensor, Medical module

## CERAMIC SUBSTRATES & COMPLEX GEOMETRY COMPONENTS

#### **MATERIALS**

#### Alumina (Al203) Ceramic Substrate

- 94 % and 96 % Alumina content available with 0.25 ~ 4 mm thickness

- High level of heat dissipation (20 W/m K)

#### Alumina (Al203) Ceramic Complex Geometry components

• 94 % and 96 % Alumina content available with multiple surfaces

#### **PROCESSES**

#### **Roll Compaction**

Spray dry ceramic powder is funneled between two carbide compaction rollers forming a green ceramic tape. The tape thickness is controlled by the spacing between the rollers and is used to feed material onto punching dies creating plates used as the array for multi-up substrate geometries.

#### Green score

Part of the roll compaction process deviates from the standard plate production in that the scribe lines and hole are created in the green tape with a second punching operation. These green score parts are punched to size before sintering making it very critical that material density and dimensions allow for the shrinkage that occurs during sintering. (Figure 5)

#### Dry press

The dry press process is generally used in the production of bi-level, irregular shaped, or thicker ceramic substrates. Many of the parts are individual single units but many parts can be manufactured with multiple substrates within an array. Design features such as holes are pressed in as the green part is formed out of spray dry powder. (Figure 6)

(Figure 5)

(Figure 6)

#### **CAPABILITIES**

#### **Stamping Dies & Compaction Tools for Green Ceramics**

Tooling is custom made in the Bourns tool shop to match the tonnage, shrinkage and form of the individual model specifications. The tooling requires a high level of precision and is primarily made from tungsten carbide. Press capability in the area ranges from 3 ton to 100 ton.

#### **APPLICATION**

Thick film substrates for use in potentiometers, MEMS sensor assemblies, multi-chip modules, and mechanical structures exposed to high temperature or where dimensional stability through temperature is critical.

**BOURNS**®

www.bourns.com

EMEA: Tel +36 88 885 877 Email eurocus@bourns.com **Asia-Pacific:** Tel +886-2 256 241 17 Email asiacus@bourns.com