# TRIPLE ELEMENT BIDIRECTIONAL THYRISTOR OVERVOLTAGE PROTECTOR

## TISP7350H3SLL Overvoltage Protector

Simultaneous 500 A 2/10 GR-1089-CORE Rating

Simultaneous 100 A 10/1000 GR-1089-CORE Rating

Ion-Implanted Breakdown Region

- Precise and Stable Voltage

#### Low Voltage Overshoot Under Surge

| Device Name   | V <sub>DRM</sub><br>V | V <sub>(BO)</sub><br>V |

|---------------|-----------------------|------------------------|

| TISP7350H3SLL | 275                   | 350                    |

#### **Rated for International Surge Wave Shapes**

- Single and Simultaneous Impulses

| Wave Shape | Standard      | I <sub>PPSM</sub><br>A |

|------------|---------------|------------------------|

| 2/10       | GR-1089-CORE  | 500                    |

| 8/20       | IEC 61000-4-5 | 350                    |

| 10/160     | TIA-968-A     | 250                    |

| 10/700     | TIA-968-A     | 200                    |

| 10/700     | ITU-T K.20/21 | 200                    |

| 10/560     | TIA-968-A     | 130                    |

| 10/1000    | GR-1089-CORE  | 100                    |

#### 3-SIP (Long Lead) Package (Top View)

#### **Device Symbol**

#### **Description**

The TISP7350H3SLL limits overvoltages between the telephone line Ring and Tip conductors and Ground. Overvoltages are normally caused by a.c. power system or lightning flash disturbances which are induced or conducted on to the telephone line.

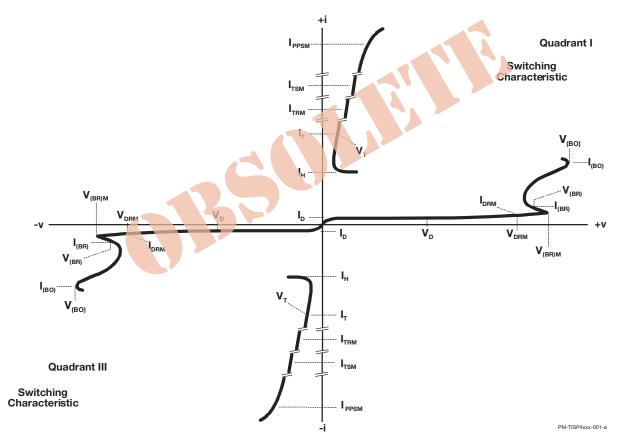

Each terminal pair, T-G, R-G and T-R, has a symmetrical voltage-triggered bidirectional thyristor protection characteristic. Overvoltages are initially clipped by breakdown clamping until the voltage rises to the breakover level, which causes the device to crowbar into a low-voltage onstate. This low-voltage on-state causes the current resulting from the overvoltage to be safely diverted through the device. The high crowbar holding current helps prevent d.c. latchup as the diverted current subsides.

These monolithic protection devices are fabricated in ion-implanted planar structures to ensure precise and matched breakover control and are virtually transparent to the system in normal operation. They are designed to voltage limit and withstand the listed international lightning surges in both polarities.

#### **How to Order**

| Device                        | Package           | Carrier          | Order As        | Marking Code | Std. Qty. |

|-------------------------------|-------------------|------------------|-----------------|--------------|-----------|

| TICDZOFOLIOCI I               | 2 CID (Long Lood) | Tape & Ammo Pack | TISP7350H3SLLAS | SP7350H3     | 2000      |

| TISP7350H3SLL 3-SIP (Long Lea |                   | Tube             | TISP7350H3SLL-S | 3F7330H3     | 1000      |

## **TISP7350H3SLL Overvoltage Protector**

### **BOURNS®**

#### Absolute Maximum Ratings, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                                         | Symbol              | Value       | Unit |

|------------------------------------------------------------------------------------------------|---------------------|-------------|------|

| Repetitive peak off-state voltage (see Note 1)                                                 | $V_{DRM}$           | ±275        | V    |

| Non-repetitive peak impulse current (see Notes 2 and 3)                                        |                     |             |      |

| 2/10 μs (GR-1089-CORE, 2/10 μs voltage wave shape)                                             |                     | ±500        |      |

| 8/20 μs (IEC 61000-4-5, 1.2/50 μs voltage wave shape, 8/20 current combination wave generator) |                     | ±350        |      |

| 10/160 μs (TIA-968-A, 10/160 μs voltage wave shape)                                            |                     | ±250        |      |

| 4/250 μs (ITU-T K.20/21, 10/700 μs voltage waveshape, dual)                                    |                     | ±225        |      |

| 0.2/310 μs (CNET I 31-24, 0.5/700 μs voltage waveshape)                                        | $I_{PPSM}$          | ±200        | Α    |

| 5/310 μs (ITU-T K.20/21, 10/700 μs voltage wave shape, single)                                 |                     | ±200        |      |

| 5/320 μs (TIA-968-A, 9/720 μs voltage wave shape)                                              |                     | ±200        |      |

| 10/560 μs (TIA-968-A, 10/560 μs voltage wave shape)                                            |                     | ±130        |      |

| 10/1000 μs (GR-1089-CORE, 10/1000 μs voltage wave shape)                                       |                     | ±100        |      |

| Non-repetitive peak on-state current (see Notes 2, 3 and 4)                                    |                     |             |      |

| 20 ms, 50 Hz (full sine wave)                                                                  |                     | 55          |      |

| 16.7 ms 60 Hz (full sine wave)                                                                 | $I_{TSM}$           | 60          | Α    |

| 1000 s, 50 Hz a.c.                                                                             |                     | 0.9         |      |

| Initial rate of rise of on-state current, exponential current ramp, maximum ramp value < 200 A | di <sub>T</sub> /dt | 400         | A/μs |

| Junction temperature                                                                           | T <sub>J</sub>      | -40 to +150 | °C   |

| Storage temperature range                                                                      | T <sub>stg</sub>    | -65 to +150 | °C   |

- NOTES: 1. Derate value at -0.13 %/°C for ambient temperatures below 25 °C.

- 2. Initially the device must be in thermal equilibrium with  $T_J = 25$  °C.

- 3. These non-repetitive rated currents are peak values of either polarity. The rated current values may be applied to any terminal pair. Additionally, both R and T terminals may have their rated current values applied simultaneously (in this case the G terminal return current will be the sum of the currents applied to the R and T terminals). The surge may be repeated after the device returns to its initial conditions.

- 4. EIA/JESD51-2 environment and EIA/JESD51-3 PCB with standard footprint dimensions connected with 5 A rated printed wiring track widths. Derate current values at -0.61 %/°C for ambient temperatures above 25 °C.

#### Electrical Characteristics for any Terminal Pair, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

|                   | Parameter                                  | Test Conditions                                                                                                                                                                                                                                                                                                                                  |                                              | Min  | Тур | Max                        | Unit  |

|-------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------|-----|----------------------------|-------|

| I <sub>DRM</sub>  | Repetitive peak off-state current          | $V_D = V_{DRM}$                                                                                                                                                                                                                                                                                                                                  | $T_A = 25 \degree C$<br>$T_A = 85 \degree C$ |      |     | ±5<br>±10                  | μА    |

| V <sub>(BO)</sub> | Breakover voltage                          | $dv/dt = \pm 750 V/ms$ , R <sub>SOURCE</sub> = 300 Ω                                                                                                                                                                                                                                                                                             |                                              |      |     | ±350                       | V     |

| V <sub>(BO)</sub> | Impulse breakover voltage                  | $dv/dt \le \pm 1000 \text{ V/μs}$ , Linear voltage ramp,<br>Maximum ramp value = $\pm 500 \text{ V}$<br>$di/dt = \pm 20 \text{ A/μs}$ , Linear current ramp,<br>Maximum ramp value = $\pm 10 \text{ A}$                                                                                                                                          |                                              |      |     | ±362                       | V     |

| I <sub>(BO)</sub> | Breakover current                          | $dv/dt = \pm 750 V/ms$ , R <sub>SOURCE</sub> = 300 Ω                                                                                                                                                                                                                                                                                             |                                              | ±100 |     | ±800                       | mA    |

| $V_{T}$           | On-state voltage                           | $I_T = \pm 5 \text{ A}, t_W = 100 \mu \text{s}$                                                                                                                                                                                                                                                                                                  |                                              |      |     | ±5                         | V     |

| I <sub>H</sub>    | Holding current                            | $I_T = \pm 5 \text{ A}$ , di/dt = $\pm 30 \text{ mA/ms}$                                                                                                                                                                                                                                                                                         |                                              | ±150 |     | ±600                       | mA    |

| dv/dt             | Critical rate of rise of off-state voltage | Linear voltage ramp, maximum ramp value < 0.85V <sub>DRM</sub>                                                                                                                                                                                                                                                                                   |                                              | ±5   |     |                            | kV/μs |

| I <sub>D</sub>    | Off-state current                          | $V_D = \pm 50 \text{ V}$                                                                                                                                                                                                                                                                                                                         | T <sub>A</sub> = 85 °C                       |      |     | ±10                        | μΑ    |

| C <sub>O</sub>    | Off-state capacitance                      | $ f = 1 \text{ MHz, } V_d = 1 \text{ V rms, } V_D = 0 \text{ V} $ $ f = 1 \text{ MHz, } V_d = 1 \text{ V rms, } V_D = -1 \text{ V} $ $ f = 1 \text{ MHz, } V_d = 1 \text{ V rms, } V_D = -2 \text{ V} $ $ f = 1 \text{ MHz, } V_d = 1 \text{ V rms, } V_D = -50 \text{ V} $ $ f = 1 \text{ MHz, } V_d = 1 \text{ V rms, } V_D = -100 \text{ V} $ |                                              |      |     | 84<br>67<br>62<br>28<br>26 | pF    |

# TISP7350H3SLL Overvoltage Protector

### BOURNS®

#### Thermal Characteristics, T<sub>A</sub> = 25 °C (Unless Otherwise Noted)

|                | Parameter                              | Test Conditions                                         | Min | Тур | Max | Unit |

|----------------|----------------------------------------|---------------------------------------------------------|-----|-----|-----|------|

| $R_{	heta JA}$ | Junction to ambient thermal resistance | EIA/JESD51-3 PCB, $I_T = I_{TSM(1000)}$<br>(see Note 5) |     |     | 50  | °C/W |

NOTE: 5. EIA/JESD51-2 environment and PCB has standard footprint dimensions connected with 5 A rated printed wiring track widths.

#### **Parameter Measurement Information**

Figure 1. Voltage-Current Characteristic for Terminal Pairs

#### **Bourns Sales Offices**

| Region        | Phone           | Fax             |

|---------------|-----------------|-----------------|

| The Americas: | +1-951-781-5500 | +1-951-781-5700 |

| Europe:       | +41-41-7685555  | +41-41-7685510  |

| Asia-Pacific: | +886-2-25624117 | +886-2-25624116 |

#### **Technical Assistance**

| Region        | Phone           | Fax             |

|---------------|-----------------|-----------------|

| The Americas: | +1-951-781-5500 | +1-951-781-5700 |

| Europe:       | +41-41-7685555  | +41-41-7685510  |

| Asia-Pacific: | +886-2-25624117 | +886-2-25624116 |

#### www.bourns.com

Bourns® products are available through an extensive network of manufacturer's representatives, agents and distributors. To obtain technical applications assistance, a quotation, or to place an order, contact a Bourns representative in your area.

Reliable Electronic Solutions